# Single Channel Operational Amplifier

LM321 is a general purpose, single channel op amp with internal compensation and a true differential input stage. This op amp features a wide supply voltage ranging from 3 V to 32 V for single supplies and  $\pm 1.5$  to  $\pm 16$  V for split supplies, suiting a variety of applications. LM321 is unity gain stable even with large capacitive loads up to 1.5 nF. LM321 is available in a space-saving TSOP-5/SOT23-5 package.

### Features

- Wide Supply Voltage Range: 3 V to 32 V

- Short Circuit Protected Outputs

- True Differential Input Stage

- Low Input Bias Currents

- Internally Compensated

- Single and Split Supply Operation

- Unity Gain Stable with 1.5 nF Capacitive Load

- This Device is Pb-Free, Halogen Free/BFR Free and is RoHS Compliant

### **Typical Applications**

- Gain Stage

- Active Filter

- Signal Processing

# **ON Semiconductor®**

www.onsemi.com

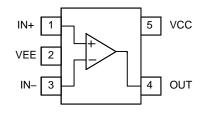

#### **PIN CONNECTION**

### MARKING DIAGRAM

ADY = Specific Device Code

- A = Assembly Location

- Y = Year

- W = Work Week

= Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

|    | Device     | Package             | Shipping <sup>†</sup> |

|----|------------|---------------------|-----------------------|

| LN | 1321SN3T1G | TSOP-5<br>(Pb-Free) | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

Table 1. ABSOLUTE MAXIMUM RATINGS (Over operating free-air temperature, unless otherwise stated)

| Parameter                              | Rating                      | Unit |

|----------------------------------------|-----------------------------|------|

| Supply Voltage                         | 36                          | V    |

| INPUT AND OUTPUT PINS                  | i                           |      |

| Input Voltage                          | V <sub>EE</sub> – 0.3 to 32 | V    |

| Input Current                          | ±10                         | mA   |

| Output Short Circuit Duration (Note 1) | Continuous                  |      |

| TEMPERATURE                            |                             |      |

| Operating Temperature                  | -40 to +125                 | °C   |

| Storage Temperature                    | -65 to +150                 | °C   |

| Junction Temperature                   | -65 to +150                 | °C   |

| ESD RATINGS (Note 2)                   |                             |      |

| Human Body Model (HBM)                 | 200                         | V    |

| Charged Device Model (CDM)             | 800                         | V    |

| Machine Model (MM)                     | 100                         | V    |

| OTHER RATINGS                          |                             |      |

| Latch-Up Current (Note 3)              | 100                         | mA   |

| MSL                                    | Level 1                     |      |

should not be assumed, damage may occur and reliability may be affected. 1. Short circuits can cause excessive heating and eventual destruction.

This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per JEDEC standard: JESD22–A114

ESD Machine Model tested per JEDEC standard: JESD22-A115

3. Latch-up Current tested per JEDEC standard: JESD78

#### Table 2. THERMAL INFORMATION (Note 4)

| Parameter           | Symbol        | Package        | Value | Unit |

|---------------------|---------------|----------------|-------|------|

| Junction to Ambient | $\theta_{JA}$ | TSOP-5/SOT23-5 | 235   | °C/W |

4. As mounted on an 80 × 80 × 1.5 mm FR4 PCB with 650 mm<sup>2</sup> and 2 oz (0.034 mm) thick copper heat spreader. Following JEDEC JESD/EIA 51.1, 51.2, 51.3 test guidelines.

#### Table 3. RECOMMENDED OPERATING CONDITIONS

| Parameter                                           | Symbol          | Range                                   | Unit |

|-----------------------------------------------------|-----------------|-----------------------------------------|------|

| Supply Voltage (V <sub>CC</sub> – V <sub>EE</sub> ) | VS              | 3 to 32                                 | V    |

| Specified Operating Range                           | T <sub>A</sub>  | -40 to 85                               | °C   |

| Common Mode Input Voltage Range                     | V <sub>CM</sub> | V <sub>EE</sub> to V <sub>CC</sub> -1.7 | V    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

### Table 4. ELECTRICAL CHARACTERISTICS – $V_S = 5 V$

(At  $T_A = +25^{\circ}$ C,  $R_L = 10 \text{ k}\Omega$  connected to mid-supply,  $V_{CM} = V_{OUT}$  = mid-supply, unless otherwise noted. **Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}$ C to 85°C, guaranteed by characterization and/or design.)

| Parameter                    | Symbol                     | Conditions                                                                                                                           | Min                                          | Тур                                          | Max                  | Unit   |

|------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------|--------|

| INPUT CHARACTERISTICS        |                            |                                                                                                                                      |                                              |                                              | L                    |        |

| Offset Voltage               | V <sub>OS</sub>            | $V_{S} = 5 V, V_{CM} = V_{EE} \text{ to } V_{CC} - 1.7 V$<br>$T_{A} = 25^{\circ}C$<br>$T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C$ |                                              | 0.3                                          | 7<br>9               | mV     |

| Offset Voltage Drift vs Temp | $\Delta V_{OS} / \Delta T$ | $T_A = -40^{\circ}C$ to $85^{\circ}C$                                                                                                | -                                            | 7                                            | _                    | μV/°C  |

| Input Bias Current           | Ι <sub>ΙΒ</sub>            | $ \begin{array}{l} T_A = 25^\circ C \\ T_A = -40^\circ C \text{ to } 85^\circ C \end{array} $                                        |                                              | -10<br>-                                     | _<br>_500            | nA     |

| Input Offset Current         | I <sub>OS</sub>            | $T_A = 25^{\circ}C$<br>$T_A = -40^{\circ}C \text{ to } 85^{\circ}C$                                                                  |                                              | 1 –                                          | _<br>150             | nA     |

| Common Mode Rejection Ratio  | CMRR                       | $V_{CM} = V_{EE}$ to $V_{CC} - 1.7$ V                                                                                                | 65                                           | 85                                           | -                    | dB     |

| Input Resistance             | R <sub>IN</sub>            | Differential<br>Common Mode                                                                                                          |                                              | 85<br>300                                    | _<br>_               | GΩ     |

| Input Capacitance            | C <sub>IN</sub>            | Differential<br>Common Mode                                                                                                          |                                              | 0.6<br>1.6                                   |                      | pF     |

| OUTPUT CHARACTERISTICS       |                            | ·                                                                                                                                    |                                              |                                              |                      |        |

| Open Loop Voltage Gain       | A <sub>VOL</sub>           |                                                                                                                                      | -                                            | 100                                          | -                    | dB     |

| Open Loop Output Impedance   | Z <sub>OUT_OL</sub>        | $f = UGBW, I_O = 0 mA$                                                                                                               | -                                            | 1,200                                        | -                    | Ω      |

| Output Voltage High          | V <sub>OH</sub>            | $R_L = 2 k\Omega$ to V <sub>EE</sub><br>$R_L = 10 k\Omega$ to V <sub>EE</sub>                                                        | V <sub>CC</sub> -1.8<br>V <sub>CC</sub> -1.8 | V <sub>CC</sub> -1.4<br>V <sub>CC</sub> -1.4 |                      | V      |

| Output Voltage Low           | V <sub>OL</sub>            | $R_L = 10 \text{ k}\Omega$ to $V_{CC}$                                                                                               | -                                            | V <sub>EE</sub> +0.8                         | V <sub>EE</sub> +1.0 | V      |

| Output Current Capability    | lo                         | Sinking Current<br>$V_S = 5 V$<br>$V_S = 15 V$                                                                                       | 10<br>10                                     | 20<br>20                                     |                      | mA     |

| Output Current Capability    | Ι <sub>Ο</sub>             | Sourcing Current<br>$V_S = 5 V$<br>$V_S = 15 V$                                                                                      | 20<br>20                                     | 40<br>40                                     | -<br>-               | mA     |

| Capacitive Load Drive        | CL                         | Phase Margin = 15°                                                                                                                   | -                                            | 1,500                                        | -                    | pF     |

| NOISE PERFORMANCE            |                            |                                                                                                                                      |                                              |                                              |                      |        |

| Voltage Noise Density        | e <sub>N</sub>             | f <sub>IN</sub> = 1 kHz                                                                                                              | -                                            | 40                                           | -                    | nV/√Hz |

| DYNAMIC PERFORMANCE          |                            |                                                                                                                                      |                                              |                                              |                      |        |

| Gain Bandwidth Product       | GBWP                       | $C_L$ = 25 pF, $R_L$ to $V_{CC}$                                                                                                     | -                                            | 750                                          | -                    | kHz    |

| Gain Margin                  | A <sub>M</sub>             | $C_L = 25 \text{ pF}, \text{ R}_L \text{ to } \text{V}_{CC}$                                                                         | -                                            | 14                                           | -                    | dB     |

| Phase Margin                 | $\alpha_{M}$               | $C_L = 25 \text{ pF}, \text{ R}_L \text{ to } \text{V}_{CC}$                                                                         | -                                            | 60                                           | -                    | 0      |

| Slew Rate                    | SR                         | $C_L = 25 \text{ pF}, R_L = \infty$                                                                                                  | -                                            | 0.3                                          | -                    | V/μs   |

| POWER SUPPLY                 |                            |                                                                                                                                      |                                              |                                              |                      |        |

| Power Supply Rejection Ratio | PSRR                       | $V_{S} = 5 V \text{ to } 32 V$                                                                                                       | 62                                           | 100                                          | _                    | dB     |

| Quiescent Current            | l <sub>Q</sub>             | No Load                                                                                                                              | -                                            | 0.25                                         | 0.5                  | mA     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

### Table 5. ELECTRICAL CHARACTERISTICS – $V_S = 32 V$

(At  $T_A = +25^{\circ}$ C,  $R_L = 10 \text{ k}\Omega$  connected to mid-supply,  $V_{CM} = V_{OUT}$  = mid-supply, unless otherwise noted. **Boldface** limits apply over the specified temperature range,  $T_A = -40^{\circ}$ C to 85°C, guaranteed by characterization and/or design.)

| Parameter                            | Symbol                     | Conditions                                                                                                                            | Min                                          | Тур                                          | Max                  | Unit   |

|--------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------|--------|

| INPUT CHARACTERISTICS                |                            | •                                                                                                                                     | •                                            | •                                            |                      |        |

| Offset Voltage                       | V <sub>OS</sub>            | $V_{S} = 32 V, V_{CM} = V_{EE} \text{ to } V_{CC} - 1.7 V$<br>$T_{A} = 25^{\circ}C$<br>$T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C$ |                                              | 0.3                                          | 7<br>9               | mV     |

| Offset Voltage Drift vs Temp         | $\Delta V_{OS} / \Delta T$ | $T_A = -40^{\circ}C$ to $85^{\circ}C$                                                                                                 | -                                            | 7                                            | -                    | μV/°C  |

| Common Mode Rejection Ratio          | CMRR                       | $V_{CM} = V_{EE}$ to $V_{CC} - 1.7$ V                                                                                                 | _                                            | 100                                          | -                    | dB     |

| OUTPUT CHARACTERISTICS               |                            |                                                                                                                                       |                                              |                                              |                      |        |

| Open Loop Voltage Gain               | A <sub>VOL</sub>           | $ \begin{array}{l} T_A = 25^\circ C \\ T_A = -40^\circ C \text{ to } 85^\circ C \end{array} $                                         | _<br>84                                      | 100<br>-                                     |                      | dB     |

| Open Loop Output Impedance           | Z <sub>OUT_OL</sub>        | f = UGBW, I <sub>O</sub> = 0 mA                                                                                                       | _                                            | 2,000                                        | -                    | Ω      |

| Output Voltage High                  | V <sub>OH</sub>            | $R_L = 2 k\Omega$ to V <sub>EE</sub><br>$R_L = 10 k\Omega$ to V <sub>EE</sub>                                                         | V <sub>CC</sub> -2.5<br>V <sub>CC</sub> -2.5 | V <sub>CC</sub> -2.0<br>V <sub>CC</sub> -1.5 |                      | V      |

| Output Voltage Low                   | V <sub>OL</sub>            | $R_L = 10 \text{ k}\Omega$ to $V_{CC}$                                                                                                | -                                            | V <sub>EE</sub> +1.0                         | V <sub>EE</sub> +1.5 | V      |

| Capacitive Load Drive                | CL                         | Phase Margin = 15°                                                                                                                    | _                                            | 1,500                                        | _                    | pF     |

| NOISE PERFORMANCE                    |                            |                                                                                                                                       |                                              |                                              |                      |        |

| Voltage Noise Density                | e <sub>N</sub>             | f <sub>IN</sub> = 1 kHz                                                                                                               | -                                            | 40                                           | -                    | nV/√Hz |

| Total Harmonic Distortion +<br>Noise | THD+N                      | $V_{S}$ = 30 V, $f_{IN}$ = 1 kHz, $R_{L}$ to $V_{CC}$                                                                                 | -                                            | 0.02                                         | -                    | %      |

| DYNAMIC PERFORMANCE                  |                            | •                                                                                                                                     | •                                            | •                                            |                      |        |

| Gain Bandwidth Product               | GBWP                       | $C_L = 25 \text{ pF}, \text{ R}_L \text{ to } \text{V}_{CC}$                                                                          | _                                            | 900                                          | _                    | kHz    |

| Gain Margin                          | A <sub>M</sub>             | $C_L = 25 \text{ pF}, \text{ R}_L \text{ to } \text{V}_{CC}$                                                                          | _                                            | 18                                           | _                    | dB     |

| Phase Margin                         | α <sub>M</sub>             | $C_L = 25 \text{ pF}, \text{ R}_L \text{ to } \text{V}_{\text{CC}}$                                                                   | _                                            | 66                                           | _                    | 0      |

| Slew Rate                            | SR                         | $C_L = 25 \text{ pF}, R_L = \infty$                                                                                                   | -                                            | 0.4                                          | -                    | V/μs   |

| POWER SUPPLY                         |                            |                                                                                                                                       |                                              |                                              |                      |        |

| Power Supply Rejection Ratio         | PSRR                       | $V_{S} = 5 V \text{ to } 32 V$                                                                                                        | 62                                           | 100                                          | -                    | dB     |

| Quiescent Current                    | Ι <sub>Q</sub>             | No Load, V <sub>S</sub> = 32 V                                                                                                        | -                                            | 0.3                                          | 1.2                  | mA     |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

### **TYPICAL CHARACTERISTICS**

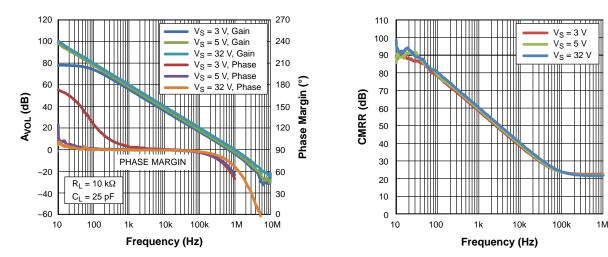

Figure 1. Open Loop Gain and Phase Margin vs. Frequency

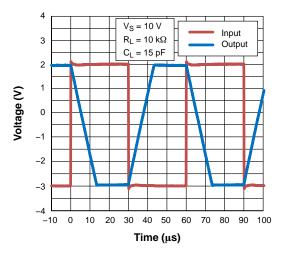

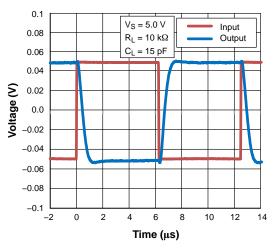

Figure 3. Inverting Large Signal Step Response

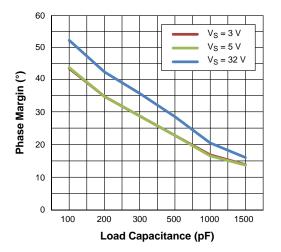

Figure 5. Phase Margin vs. Load Capacitance

Figure 2. CMRR vs. Frequency

Figure 4. Inverting Small Signal Step Response

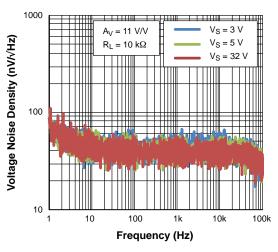

Figure 6. Voltage Noise Density vs. Frequency

### **TYPICAL CHARACTERISTICS**

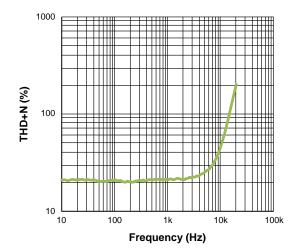

Figure 7. THD+N vs. Frequency

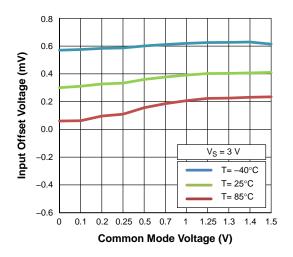

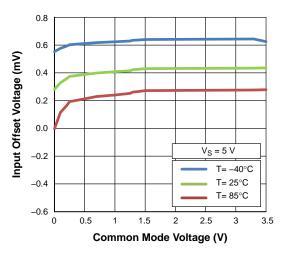

Figure 9. Input Offset Voltage vs. Common Mode Voltage at 3 V Supply

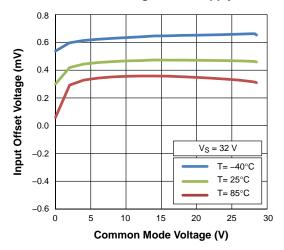

Figure 11. Input Offset Voltage vs. Common Mode Voltage at 32 V Supply

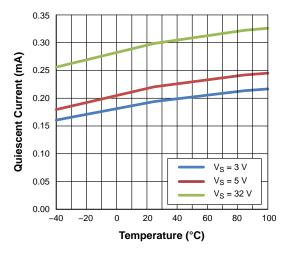

Figure 8. Quiescent Current vs. Temperature

Figure 10. Input Offset Voltage vs. Common Mode Voltage at 5 V Supply

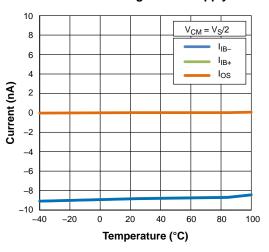

Figure 12. Input Bias and Offset Current vs. Temperature

### **TYPICAL CHARACTERISTICS**

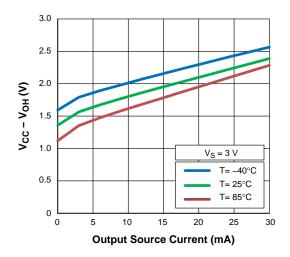

Figure 13. High Level Output Voltage Swing vs. Output Current at 3 V Supply

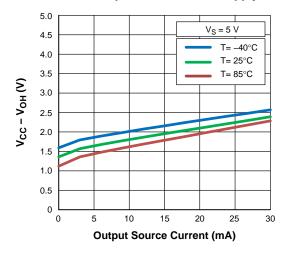

Figure 15. High Level Output Voltage Swing vs. Output Current at 5 V Supply

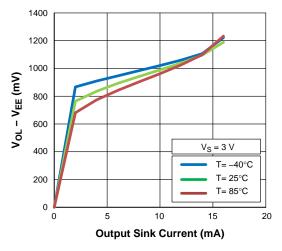

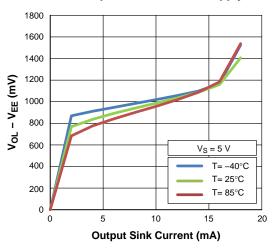

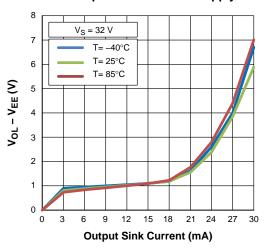

Figure 14. Low Level Output Voltage Swing vs. Output Current at 3 V Supply

Figure 16. Low Level Output Voltage Swing vs. Output Current at 5 V Supply

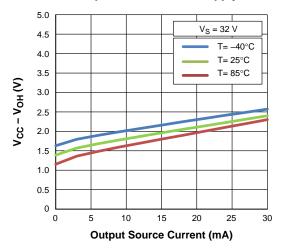

Figure 18. Low Level Output Voltage Swing vs. Output Current at 5 V Supply32

### APPLICATION INFORMATION

#### **CIRCUIT DESCRIPTION**

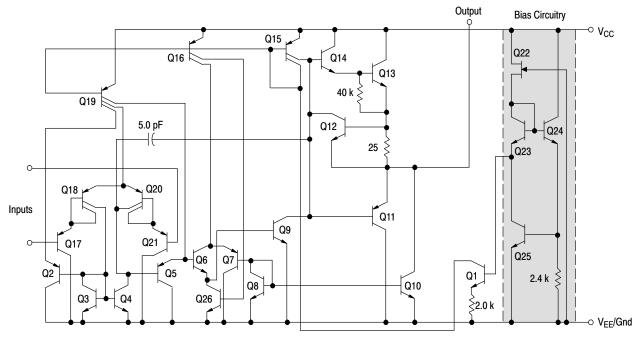

The LM321 is made using two internally compensated, two-stage operational amplifiers. The first stage of each consists of differential input devices Q20 and Q18 with input buffer transistors Q21 and Q17 and the differential to single ended converter Q3 and Q4. The first stage performs not only the first stage gain function but also performs the level shifting and transconductance reduction functions. By reducing the transconductance, a smaller compensation capacitor (only 5.0 pF) can be employed, thus saving chip area. The transconductance reduction is accomplished by splitting the collectors of Q20 and Q18. Another feature of this input stage is that the input common mode range can include the negative supply or ground, in single supply operation, without saturating either the input devices or the differential to single–ended converter. The second stage consists of a standard current source load amplifier stage.

Each amplifier is biased from an internal-voltage regulator which has a low temperature coefficient thus giving each amplifier good temperature characteristics as well as excellent power supply rejection.

Figure 19. LM321 Representative Schematic Diagram

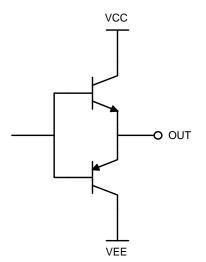

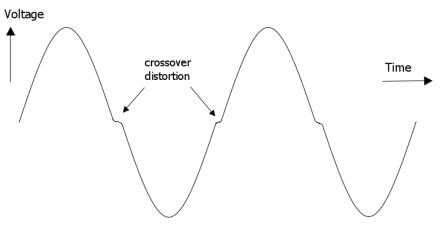

LM321 has a class B output stage, which is comprised of push-pull transistors. This type of output is inherently subject to crossover distortion near mid-rail where neither push or pull transistors are conducting. Several techniques can be used to minimize crossover distortion. Connecting the output load to either the positive or negative supply rail instead of mid-rail can reduce the crossover distortion. Additionally, increasing the load resistance relatively decreases the amount of crossover distortion.

Figure 20. Simplified Class B Output

Figure 21. Sine wave with crossover distortion

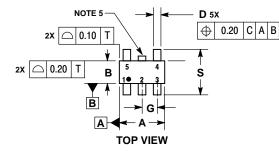

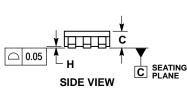

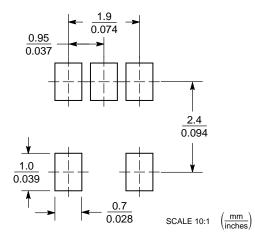

#### PACKAGE DIMENSIONS

TSOP-5 **CASE 483 ISSUE L**

NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME

- Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS. 2 3

- 4

- CONTROLLING DIMENSION: MILLIMETERS. MAXIMUM LEAD THICKNESS INCLUDES LEAD FINISH THICKNESS. MINIMUM LEAD THICKNESS IS THE MINIMUM THICKNESS OF BASE MATERIAL. DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS. SHALL NOT EXCEED 0.15 PER SIDE. DIMENSION A. OPTIONAL CONSTRUCTION: AN ADDITIONAL

- OPTIONAL CONSTRUCTION: AN ADDITIONAL TRIMMED LEAD IS ALLOWED IN THIS LOCATION. 5 TRIMMED LEAD NOT TO EXTEND MORE THAN 0.2 FROM BODY.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN MAX     |      |  |  |

| Α   | 3.00        | BSC  |  |  |

| В   | 1.50        | BSC  |  |  |

| С   | 0.90        | 1.10 |  |  |

| D   | 0.25        | 0.50 |  |  |

| G   | 0.95 BSC    |      |  |  |

| Н   | 0.01        | 0.10 |  |  |

| J   | 0.10        | 0.26 |  |  |

| κ   | 0.20        | 0.60 |  |  |

| М   | 0 °         | 10 ° |  |  |

| S   | 2.50        | 3.00 |  |  |

#### SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the unarregistered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed Solicito wins emic.com/site/pdf/Patent-Marking.pdf. Scill\_CC reserves the right to make changes without further notice to any products herein. Scill\_CC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters, including "Typicals" must be validated for each and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical inplant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative